# UNITED STATES INTERNATIONAL TRADE COMMISSION

# Washington, D.C.

In the Matter of

CERTAIN POWER INVERTERS AND CONVERTERS, VEHICLES CONTAINING THE SAME, AND COMPONENTS THEREOF

Inv. No. 337-TA-1267

# FINAL INITIAL DETERMINATION ON VIOLATION OF SECTION 337

Administrative Law Judge Monica Bhattacharyya

(August 12, 2022)

**Appearances**:

For Complainant Arigna Technology Limited:

Matthew R. Berry, Rachel S. Black, Andres Healy, John Schiltz, Nicholas Crown, and Danielle Nicholson of Susman Godfrey LLP in Seattle, WA; Oleg Elkhunovich of Susman Godfrey LLP in Los Angeles, CA; Bryce T. Barcelo and Tom DelRosario of Susman Godfrey LLP in Houston, TX; Reza Mirzaie and Brett Cooper of Russ August & Kabat in Los Angeles, CA; and Matthew D. Aichele and Jonathan Link of Russ August & Kabat in Washington, DC.

For Respondents Volkswagen AG, Volkswagen Group of America, Inc., Audi AG, Audi of America, LLC, Bentley Motors Limited, Bentley Motors, Inc., Automobili Lamborghini S.p.A., and Automobili Lamborghini America, LLC:

Mareesa A. Frederick, J. Preston Long, Gerald F. Ivey, Amy Fulton, and Matthew R. Ritter of Finnegan, Henderson, Farabow, Garrett & Dunner LLP in Washington, DC; and John M. Mulcahy, Elliott Cook, Yi Yu, and Dan Jordan of Finnegan, Henderson, Farabow, Garett & Dunner LLP in Reston, VA.

# For Respondents Bayerische Motoren Worke AG and BMW of North America, LLC:

Smith R. Brittingham, R. Benjamin Cassady, Michael J. Aragon, Matthew C. Berntsen, Michael J. McLaughlin, and Lionel M. Lavenue of Finnegan, Henderson, Farabow, Garrett & Dunner LLP in Washington, DC; Robert Fernandes and Sneha Nyshadham of Finnegan, Henderson, Farabow, Garrett & Dunner in Palo Alto, CA; and Max Mauldin of Finnegan, Henderson, Farabow, Garrett & Dunner in Atlanta, GA

# For Respondent General Motors LLC:

Michael J. McKeon, Christian A. Chu, and Jared Hartzman of Fish & Richardson in Washington, DC; Tim Rawson of Fish & Richardson in San Diego, CA; Leeron Kalay of Fish & Richardson in Redwood City, CA; and Joe Herriges of Fish & Richardson in Minneapolis, MN.

# For Respondents Daimler AG and Mercedes-Benz USA, LLC:

Celine J. Crowson, Joseph J. Raffetto, Scott Hughes, Anna Kurian Shaw, Ryan J. Stephenson, Nicholas W. Rotz, Yi Sally Zhang, Michael Kosuge, and Eric Wang of Hogan Lovells US LLP in Washington, DC; Lisa Dong of Hogan Lovells US LLP in Denver, CO; and Helen Y. Trac of Hogan Lovells US LLP in San Francisco, CA.

# For the Office of Unfair Import Investigations:

W. Peter Guarnieri and David O. Lloyd of the U.S. International Trade Commission in Washington, DC.

Pursuant to the Notice of Investigation (EDIS Doc. ID 745316), 86 Fed. Reg. 34042-43 (Jun. 28, 2021), and Commission Rule 210.42, this is the administrative law judge's final initial determination in the matter of *Certain Power Inverters and Converters, Vehicles Containing the Same, and Components Thereof,* Commission Investigation No. 337-TA-1267. 19 C.F.R. § 210.42(a)(1)(i).

For the reasons discussed herein, it is the undersigned's final initial determination that there has been no violation of section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. § 1337, in the importation into the United States, the sale for importation, and/or the sale within the United States after importation of certain power inverters and converters used in automobiles, components thereof, and automobiles containing those power inverters or converters by reason of infringement of claims of U.S. Patent No. 8,247,867 or U.S. Patent No. 8,289,082.

# TABLE OF CONTENTS

| I.   | BACKGROUND                               | . 1 |

|------|------------------------------------------|-----|

| А.   | Procedural History                       | . 1 |

| В.   | The Parties                              | 3   |

| C.   | Products at Issue                        | 5   |

| D.   | Asserted Patents                         | 6   |

| E.   | Witness Testimony                        | 7   |

| II.  | JURISDICTION                             | 9   |

| А.   | Subject Matter Jurisdiction              | 9   |

| В.   | Personal Jurisdiction                    | 9   |

| C.   | In Rem Jurisdiction                      | 10  |

| III. | LEGAL STANDARDS                          | 10  |

| A.   | Infringement                             | 10  |

| В.   | Claim Construction                       | 11  |

| C.   | Invalidity                               | 12  |

| D.   | Domestic Industry                        | 15  |

| IV.  | U.S. PATENT NO. 8,289,082                | 17  |

| A.   | Specification                            | 18  |

| В.   | Asserted claims                          | 19  |

| C.   | Claim Construction                       | 20  |

| D.   | Level of Ordinary Skill in the Art       | 31  |

| E.   | Infringement                             | 31  |

| F.   | Domestic Industry—Technical prong        | 56  |

| G.   | Domestic Industry—Economic prong         | 64  |

| Η.   | Invalidity                               |     |

| V.   | U.S. PATENT NO. 8,247,867 1              | 18  |

| А.   | Specification1                           | 18  |

| В.   | Asserted claims 1                        | 20  |

| C.   | Claim Construction                       | 21  |

| D.   | Level of Ordinary Skill in the Art1      | 22  |

| E.   | Importation of Certain Accused Products1 | 22  |

| F.   | Infringement 1                           | 35  |

| G.   | Domestic Industry 1                      | 59  |

| H.   | Invalidity1                              |     |

| VI.  | CONCLUSIONS OF LAW 1                     | 98  |

| Tr.      | Hearing Transcript                       |

|----------|------------------------------------------|

| Dep. Tr. | Deposition Transcript                    |

| JX       | Joint Exhibit                            |

| СХ       | Complainants' exhibit                    |

| СРХ      | Complainants' physical exhibit           |

| CDX      | Complainants' demonstrative exhibit      |

| RX       | Respondents' exhibit                     |

| RPX      | Respondents' physical exhibit            |

| RDX      | Respondents' demonstrative exhibit       |

| СРНВ     | Complainants' pre-hearing brief          |

| CIB      | Complainants' initial post-hearing brief |

| CRB      | Complainants' post-hearing reply brief   |

| RPHB     | Respondents' pre-hearing brief           |

| RIB      | Respondents' initial post-hearing brief  |

| RRB      | Respondents' post-hearing reply brief    |

| SPHB     | Staff's pre-hearing brief                |

| SIB      | Staff's initial post-hearing brief       |

| SRB      | Staff's post-hearing reply brief         |

The following abbreviations may be used in this Initial Determination:

# I. BACKGROUND

#### A. Procedural History

The Commission instituted this investigation in response to a complaint filed by Complainant Arigna Technology Limited ("Arigna") on May 21, 2021 (the "Complaint," EDIS Doc. ID 743107), and supplemented on May 26, June 9, and June 10, 2021. Notice of Investigation at 1, EDIS Doc. No. 745316 (Jun. 23, 2021); 86 Fed. Reg. 34042 (Jun. 28, 2021). The complaint alleges violations of section 337 of the Tariff Act of 1930, as amended, by reason of infringement of certain claims of U.S. Patent No. 8,247,867 ("the '867 patent") and U.S. Patent No. 8,289,082 ("the '082 patent"). Id. The Commission ordered institution of this investigation to determine "whether there is a violation of subsection (a)(1)(B) of section 337 in the importation into the United States, the sale for importation, or the sale within the United States after importation of certain products . . . by reason of infringement of one or more of claims 1, 2, 8, and 9 of the '867 patent and claims 1-6, 13, 17-22, and 29 of the '082 patent; and whether an industry in the United States exists as required by subsection (a)(2) of section 337." Id. at 2. The investigation was instituted upon publication of the Notice of Investigation in the Federal Register on Monday, June 28, 2021. 86 Fed. Reg. 34042-43. The Notice of Investigation named the following entities as Respondents: Volkswagen AG, Volkswagen Group of America, Inc., Audi AG, Audi of America, Bentley Motors Limited, Bentley Motors, Inc., Automobili Lamborghini America, LLC, Automobili Lamborghini S.p.A., Porsche AG, Porsche Cars North America, Inc., Daimler AG, Mercedes-Benz USA, LLC, Bayerische Motoren Werke AG, BMW of North America, LLC, General Motors Company, and General Motors LLC. Id. The Office of Unfair Import Investigations is also a party to the investigation. Id.

Pursuant to Order No. 5, EDIS Doc. ID. 747201 (Jul. 19, 2021), the target date of this investigation was originally set to be November 28, 2022. *See* Comm'n Notice, EDIS Doc. ID 748429 (Aug. 2, 2021). On September 13, 2021, the investigation was assigned by former Chief Administrative Law Judge Bullock to the undersigned. *See* Notice to the Parties, EDIS Doc. ID 751528 (Sept. 13, 2021).

A *Markman* hearing was held on December 1, 2021. *See Markman* Tr., EDIS Doc. ID 757895 (Dec. 1, 2021). A *Markman* order issued on January 18, 2022, construing certain terms of the asserted claims of the '867 patent and '082 patent. Order No. 30, EDIS Doc. ID 760711.

Pursuant to Order No. 23, EDIS Doc. ID 758896 (Dec. 20, 2021), Arigna withdrew its allegations against Respondent General Motors Company. *See* Comm'n Notice, EDIS Doc. ID 760698 (Jan. 18, 2022). Pursuant to Order No. 37 (Feb. 18, 2022), Arigna withdrew its allegations of infringement with respect to the '867 patent against Respondents BMW AG and BMW of North America, LLC. *See* Comm'n Notice, EDIS Doc. ID 765434 (Mar. 15, 2022). Pursuant to Order No. 50 (Apr. 6, 2022), Arigna withdrew its allegations of infringement with respect to claims 2-6 and 18-22 of the '082 patent and claims 1, 2, and 9 of the '867 patent. *See* Comm'n Notice, EDIS Doc. ID 769133 (Apr. 25, 2022). Pursuant to Order No. 53 (Apr. 29, 2022), Respondents Porsche AG and Porsche Cars North America, Inc. were terminated from the investigation pursuant to a settlement agreement. *See* Comm'n Notice, EDIS Doc. ID 770942 (May 17, 2022).

An evidentiary hearing was held on April 4-8, 2022. The parties filed initial post-hearing briefs on April 25, 2022, and filed post-hearing reply briefs on May 4, 2022. Pursuant to Order No. 54, the target date was extended by two weeks to December 12, 2022. Order No. 54, EDIS Doc. ID 776314 (Jul. 27, 2022).

# B. The Parties

#### 1. Complainant

The complainant is Arigna Technology Limited ("Arigna"). Notice of Investigation at 2. Arigna is an Irish company with an address in Dublin, Ireland. Complaint ¶ 7. Arigna is the owner of both the '867 patent and the '082 patent by assignment. *See* JX-00001 ('867 patent assignment abstract); JX-00003 ('867 patent assignment records); JX-00005 ('082 patent assignment records).

#### 2. Third-Party Licensee

Third-party Microchip Technology, Inc. ("Microchip") is a U.S. company headquartered in Chandler, Arizona. *See* CX-00440 (Microchip Form 10-K). Microchip was a previous assignee of the '082 patent. *See* JX-00005. Arigna has granted Microchip a license to the '082 patent and the '867 patent. CX-00097C (Arigna-Microchip Agreement, June 26, 2020).

#### 3. Respondents

The respondents are vehicle manufacturers. See RIB at 4.

Respondent Bayerische Motoren Werke AG ("BMW AG") is a German company with its principal place of business in Munich, Germany. BMW AG Answer to Complaint at ¶ 15, EDIS Doc. ID 748293 (Jul. 29, 2021). BMW of North America, LLC ("BMW NA") is an indirect subsidiary of BMW AG (together, BMW AG and BMW NA are "BMW"), with a principal place of business in Woodcliff Lake, New Jersey. BMW NA Answer to Complaint at ¶ 15, EDIS Doc. ID 748281 (Jul. 29, 2021).

Respondent General Motors LLC ("GM" or "General Motors") is a Delaware corporation headquartered in Detroit, Michigan. GM Answer to Complaint at ¶ 21, EDIS Doc. ID 748267 (Jul. 29, 2021).

Respondent Daimler AG ("Daimler") is a German corporation headquartered in Stuttgart, Germany. Daimler Answer to Complaint at ¶ 27, EDIS Doc. ID 748569 (Jul. 29, 2021). Respondent Mercedes-Benz USA, LLC ("MBUSA") is a Delaware company headquartered in Sandy Springs, Georgia. MBUSA Answer to Complaint at ¶ 27, EDIS Doc. ID 748564 (Jul. 29, 2021). MBUSA is owned by Daimler International Nederland B.V., which is a wholly-owned subsidiary of Daimler (together, Daimler and MBUSA are "Mercedes"). *See* CX-02300C.

Respondent Volkswagen AG is a German corporation headquartered in Wolfsburg, Germany. Volkswagen Answer to Complaint at ¶ 12, EDIS Doc. ID 748269 (Jul. 29, 2021). Respondent Audi AG is a German corporation located in Ingolstadt, Germany. Id. Respondent Audi of America, LLC is a Delaware corporation located in Herndon, Virginia. Id. Respondent Bentley Motors Limited is a British corporation located in Cheshire, England. Id. at ¶ 18. Respondent Bentley Motors, Inc. is a New York corporation located in Herndon, Virginia. Respondent Volkswagen Group of America, Inc. is a New Jersey corporation located in Herndon, Virginia. Id. Respondent Automobili Lamborghini S.p.A., is an Italian corporation located in Bolognese, Italy. Id. at ¶ 24. Automobili Lamborghini S.p.A is a wholly owned subsidiary of Id. Automobili Lamborghini America, LLC is a Delaware corporation located in Herndon, Virginia. Id. Automobili Lamborghini America, LLC is a wholly owned subsidiary of . Id. Respondents Volkswagen AG, Volkswagen Group of America, Inc., Audi AG, Audi of America, LLC, Bentley Motors Limited, Bentley Motors, Inc., Automobili Lamborghini S.p.A., and Automobili Lamborghini America, LLC are collectively the "Volkswagen Group."

# C. Products at Issue

The products at issue are "power inverters and converters used in automobiles, components thereof, and automobiles containing those power inverters or converters." Notice of Investigation at 2. Arigna accuses different sets of products of infringing claims of the '082 patent and '867 patent. CIB at 7-9. Arigna also relies on different sets of products for the domestic industry requirement. *Id.* at 9.

# 1. Accused Products – '082 Patent

Arigna accuses the Hella 48V Converter (containing the Analog Devices AD8417 chip), the Bosch 48V Converter and Bosch LEB450 Inverter (containing the Analog Devices AD8418 chip) of infringing claims 1, 13, 17, and 29 of the '082 patent. CIB at 7-8; Tr. (Sechen) at 165:12-18. The Hella 48V Converter is alleged to be used in certain Mercedes vehicles. CIB at 7-8. The Bosch 48V Converter is alleged to be used in certain Volkswagen vehicles. *Id*. The Bosch LEB450 Inverter is alleged to be used in certain BMW vehicles. *Id*.

## 2. Accused Products – '867 Patent

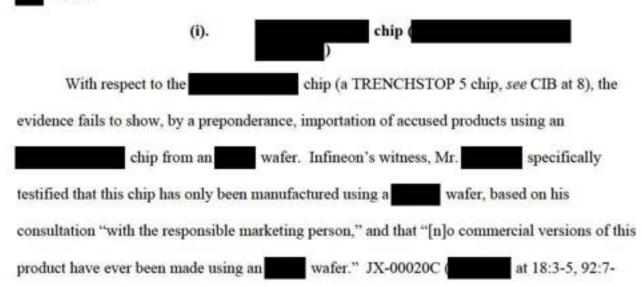

Arigna accuses the

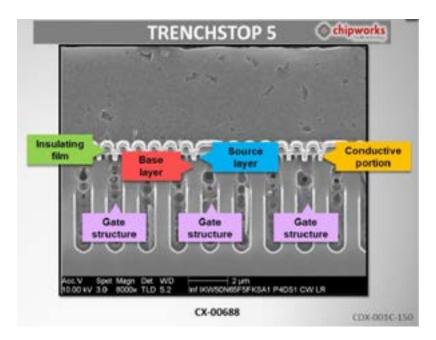

and certain Respondents' electric vehicles containing these inverters, and components thereof, of infringing claim 8 of the '867 patent. CIB at 8-9; Tr. (Sechen) at 312:15-313:5 and CDX-001C.141. Each of the accused inverters and vehicles includes an Infineon IGBT chip. *Id*.<sup>1</sup>

The accused

contains an Infineon TRENCHSTOP 5 chip with

part number

. Id. The accused

<sup>&</sup>lt;sup>1</sup> The term "IGBT" means "Insulated Gate Bipolar Transistor." Tr. (Sechen) at 314:7-9; Tr. (Resp. Opening) at 65. The accused chips are IGBTs. *See* Tr. (Sechen) at 448:12-14; RX-0713C (Decl.) ¶¶ 3, 20.

| Inverter,     | contain                                                                  |

|---------------|--------------------------------------------------------------------------|

|               |                                                                          |

|               | The accused                                                              |

|               | is used in the accused GM Cadillac Lyriq (2022+ models), and the accused |

|               | is used in the accused GM Hummer EV (models 2021+) and                   |

| BrightDrop EV | 500 (models 2021+). Id. The accused                                      |

|               | are used in the accused VW ID.4                                          |

| (models       | , Audi (models ), and Audi (models                                       |

| ). Id.        |                                                                          |

# 3. Domestic Industry Products

The domestic industry products for the '082 patent are Microchip's ATMXT540S and ATMXT336S MaXTouch controllers. CIB at 9. The domestic industry products for the '867 patent are certain Microchip Trench FET products in development, which are identified by their mask numbers:

# D. Asserted Patents

The '082 patent is titled "Circuit and Method for Adjusting an Offset Output Current for an Input Current Amplifier" and was originally assigned to Atmel Corporation, a predecessor-ininterest to Microchip. *See* JX-00005 ('082 assignment records).

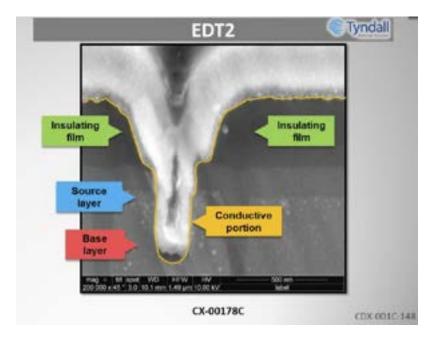

<sup>&</sup>lt;sup>2</sup> "EDT2" and "TRENCHSTOP 5" are two categories of Infineon IGBT chips. RX-0713C ( Decl.) ¶ 3, 20.

The '867 patent is titled "Semiconductor Device" and was originally assigned to Mitsubishi Electric Corporation ("Mitsubishi"). JX-00004. Arigna acquired ownership of the '867 patent from Mitsubishi on February 13, 2020. JX-00001.

## E. Witness Testimony

The undersigned received testimonial evidence in this investigation in the form of live testimony and deposition designations.

# 1. Hearing Testimony

Arigna relies on the testimony of Dr. Carl Sechen, who was admitted as an expert in the field of electrical engineering, including analog circuit and semiconductor design and fabrication. Tr. at 154:20-155:13. Dr. Sechen offered testimony regarding the alleged infringement and satisfaction of the technical prong of the domestic industry requirement with respect to the asserted claims of the '082 patent and '867 patent,. *Id.* at 148-611. He also offered testimony regarding the validity of the asserted claims of the '082 patent and '867 patent and '867 patent. *Id.* at 1221-1310. Arigna also relies on the testimony of Mr. Gregory Smith, who was admitted as an expert in the field of economics to offer economic analysis on issues related to domestic industry, public interest, and remedy. Tr. at 612-712 (expert qualification at 616:10-25).

Respondents rely on the testimony of Dr. John Bravman, who was admitted as an expert in the field of semiconductor device structures, semiconductor device fabrication, semiconductor device imaging, and characterization and related technology and offered testimony regarding the '867 patent. Tr. at 714-940 (expert qualification at 719:8-20). Respondents also rely on the testimony of Mr. Brett Reed, who was admitted as an expert in economics, particularly with issues relevant to section 337 investigations. Tr. at 942-989 (expert qualification at 944:22-945:10). Respondents further rely on the testimony of Dr. John Graham, who was admitted as an

expert in the area of public policy, public health, cost-benefit analysis, regulatory and policy analysis relating to electrified vehicles. Tr. at 990-1025 (expert qualification at 993:1-15). Respondents also rely on the testimony of Dr. Nareg Sinenian, who was admitted as an expert in the field of design and analysis of electronic circuits, including amplifiers and offered testimony regarding the alleged infringement of the asserted claims of the '082 patent. Tr. at 1026-1111 (expert qualification at 1032:9-21). Respondents' final witness was Dr. Shoukri Souri, who was admitted as an expert in the field of design and analysis of electronic circuits, including amplifiers and offered testimony regarding the asserted invalidity of the '082 patent. Tr. at 1112-1221 (expert qualification at 1116:22-1117:6).

# 2. Deposition Designations and Declarations

The parties submitted several designated deposition transcripts and third-party declarations, which were received in evidence without a sponsoring witness. Tr. at 527:1-17.

| Exhibit   | Description                                                         |  |  |

|-----------|---------------------------------------------------------------------|--|--|

| JX-00010C | 2021-12-08 Designated Deposition Transcript of                      |  |  |

| JX-00011C | 2021-12-02 Designated Deposition Transcript of                      |  |  |

| JX-00012C | 2021-12-08 Designated Deposition Transcript of Thomas Danieli       |  |  |

| JX-00013C | 2021-12-10 Designated Deposition Transcript of                      |  |  |

| JX-00014C | 2021-12-14 Designated Deposition Transcript of Stephanus Duvenhage  |  |  |

| JX-00015C | 2021-12-03 Designated Deposition Transcript of                      |  |  |

| JX-00016C | 2021-12-10 Designated Deposition Transcript of Rudy Jaramillo       |  |  |

| JX-00017C | 2021-12-08 Designated Deposition Transcript of Paul Kelley          |  |  |

| JX-00018C | 2021-12-14 Designated Deposition Transcript of Leonardo Laviola     |  |  |

| JX-00019C | 2021-12-09 Designated Deposition Transcript of                      |  |  |

| JX-00020C | 2021-12-07 Designated Deposition Transcript of 1                    |  |  |

| JX-00021C | 2021-12-10 Designated Deposition Transcript of                      |  |  |

| JX-00022C | 2021-11-23 Designated Deposition Transcript of                      |  |  |

| JX-00023C | 2021-12-09 Designated Deposition Transcript of Michael Rocco        |  |  |

| JX-00024C | 2022-01-19 Designated Deposition Transcript of                      |  |  |

| JX-00025C | 2021-12-14 Designated Deposition Transcript of Patrick Stowe        |  |  |

| JX-00026C | 2021-12-20 Designated Deposition Transcript of Gerald Padian        |  |  |

| CX-00519C | Declaration of Steve Liu on behalf of Delta Electronics             |  |  |

| CX-00520C | Declaration of Alasdair Alexander on behalf of Analog Devices, Inc. |  |  |

| CX-00521C | Declaration of                                                      |  |  |

| CX-00522C | Declaration of Carlos Sanchez on behalf of Analog Devices, Inc. |

|-----------|-----------------------------------------------------------------|

| CX-00523C | Declaration of Seungyu Yoon on behalf of LG Magna               |

#### **II. JURISDICTION**

In order to have the power to decide a case, a court or agency must have both subject matter jurisdiction and jurisdiction over either the parties or the property involved. 19 U.S.C. § 1337; *Certain Steel Rod Treating Apparatus and Components Thereof*, Inv. No. 337-TA-97, Commission Memorandum Opinion, 215 U.S.P.Q. 229, 231 (1981).

# A. Subject Matter Jurisdiction

Section 337 confers subject matter jurisdiction on the Commission to investigate, and if appropriate, to provide a remedy for, unfair acts and unfair methods of competition in the importation, the sale for importation, or the sale after importation of articles into the United States. *See* 19 U.S.C. §§ 1337(a)(1)(B) and (a)(2). The Commission has subject matter jurisdiction over this investigation based on Arigna's allegations that the accused products are imported into the United States. CIB at 10; RIB at 15; *see Amgen Inc. v. Int'l Trade Comm'n*, 565 F.3d 846, 854 (Fed. Cir. 2009) ("In this case, the Commission had jurisdiction as a result of Amgen's allegation that Roche imported an article . . . covered by the claims of a valid and enforceable United States patent.").

## **B.** Personal Jurisdiction

Respondents have submitted to the personal jurisdiction of the Commission by answering the Complaint and Notice of Investigation, participating in discovery, appearing at hearings, and filing motions and briefs. *See Certain Miniature Hacksaws*, Inv. No. 337-TA-237, USITC Pub. No. 1948, Initial Determination at 4, 1986 WL 379287, \*1 (Oct. 15, 1986), *not reviewed in relevant part by* Comm'n Action and Order, 1987 WL 450871 (Jan. 15, 1987). Respondents do not contest that the Commission has *in personam* jurisdiction over them. RIB at 15.

# C. In Rem Jurisdiction

The Commission has *in rem* jurisdiction over accused products by virtue of their importation into the United States. *See Sealed Air Corp. v. U.S. Int'l Trade Comm'n*, 645 F.2d 976, 985-86 (C.C.P.A. 1981) (holding that the ITC's jurisdiction over imported articles is sufficient to exclude such articles). Except for a dispute regarding certain types of accused chips used in the accused VW vehicles, Respondents have admitted to the importation of the accused vehicles and/or components. *See* CX-00515C (GM Joint Stipulation of Facts); CX-00027C (Audi Interrogatory Response); CX-01948C (BMW Joint Stipulation); CX-02253C (Bentley Interrogatory Response); CX-00120C (Lamborghini Interrogatory Response); CX-02300C (Mercedes Interrogatory Response); CX-02370C (VW Interrogatory Response).<sup>3</sup>

#### III. LEGAL STANDARDS

#### A. Infringement

Section 337(a)(1)(B)(i) prohibits "the importation into the United States, the sale for importation, or the sale within the United States after importation by the owner, importer, or consignee, of articles that – (i) infringe a valid and enforceable United States patent or a valid and enforceable United States copyright registered under title 17." 19 U.S.C. §1337(a)(1)(B)(i). The Commission has held that the word "infringe" in Section 337(a)(1)(B)(i) "derives its legal meaning from 35 U.S.C. § 271, the section of the Patent Act that defines patent infringement." *Certain Elec. Devices with Image Processing Sys., Components Thereof, and Associated Software*, Inv. No. 337-TA-724, Comm'n Op. at 13-14, EDIS Doc. ID 467105 (December 21, 2011).

<sup>&</sup>lt;sup>3</sup> VW disputes whether certain types of accused chips have been imported, as discussed in Part V.E infra.

Infringement must be proven by a preponderance of the evidence. *SmithKline*

*Diagnostics, Inc. v. Helena Labs. Corp.*, 859 F.2d 878, 889 (Fed. Cir. 1988). The preponderance of the evidence standard "requires proving that infringement was more likely than not to have occurred." *Warner-Lambert Co. v. Teva Pharm. USA, Inc.*, 418 F.3d 1326, 1341 n.15 (Fed. Cir. 2005). Literal infringement requires the patentee to prove that the accused device meets each and every limitation of the asserted claim(s). *Frank's Casing Crew & Rental Tools, Inc. v. Weatherford Int'l, Inc.*, 389 F.3d 1370, 1378 (Fed. Cir. 2004). "If even one limitation is missing or not met as claimed, there is no literal infringement." *Elkay Mfg. Co. v. EBCO Mfg. Co.*, 192 F.3d 973, 980 (Fed. Cir. 1999). Literal infringement is a question of fact. *Finisar Corp. v. DirecTV Grp., Inc.*, 523 F.3d 1323, 1332 (Fed. Cir. 2008).

## **B.** Claim Construction

"An infringement analysis entails two steps. The first step is determining the meaning and scope of the patent claims asserted to be infringed. The second step is comparing the properly construed claims to the device accused of infringing." *Markman v. Westview Instruments, Inc.*, 52 F.3d 967, 976 (Fed. Cir. 1995) (en banc), *aff'd*, 517 U.S. 370 (1996) (citation omitted). "[T]he construction of claims is simply a way of elaborating the normally terse claim language[] in order to understand and explain, but not to change, the scope of the claims." *Embrex, Inc. v. Serv. Eng'g Corp.*, 216 F.3d 1343, 1347 (Fed. Cir. 2000) (alterations in original) (quoting *Scripps Clinic v. Genentech, Inc.*, 927 F.2d 1565, 1580 (Fed. Cir. 1991)). "[O]nly those [claim] terms need be construed that are in controversy, and only to the extent necessary to resolve the controversy." *Vivid Techs., Inc. v. Am. Sci. & Eng'g. Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999). The words of a claim "'are generally given their ordinary and customary meaning," which is "the meaning that the term would have to a person of ordinary skill in art"

as of the date that the patent application was filed. *Phillips v. AWH Corp.*, 415 F.3d 1303, 1312-13 (Fed. Cir. 2005) (en banc) (quoting *Vitronics Corp. v. Conceptronic, Inc.*, 90 F.3d 1576, 1582 (Fed. Cir. 1996)).

## C. Invalidity

It is the respondents' burden to prove invalidity, and the burden of proof never shifts to the patentee to prove validity. *Scanner Techs. Corp. v. ICOS Vision Sys. Corp. N.V.*, 528 F.3d 1365, 1380 (Fed. Cir. 2008). "Under the patent statutes, a patent enjoys a presumption of validity, *see* 35 U.S.C. § 282, which can be overcome only through facts supported by clear and convincing evidence . . . ." *SRAM Corp. v. AD-II Eng'g, Inc.*, 465 F.3d 1351, 1357 (Fed. Cir. 2006); *see also Microsoft Corp. v. i4i Ltd. P'ship*, 564 U.S. 91, 100-114 (2011) (upholding the "clear and convincing" standard for invalidity).

The clear and convincing evidence standard placed on the party asserting an invalidity defense requires a level of proof beyond the preponderance of the evidence. Although not susceptible to precise definition, "clear and convincing" evidence has been described as evidence that produces in the mind of the trier of fact "an abiding conviction that the truth of a factual contention is 'highly probable." *Price v. Symsek*, 988 F.2d 1187, 1191 (Fed. Cir. 1993) (quoting *Buildex, Inc. v. Kason Indus., Inc.*, 849 F.2d 1461, 1463 (Fed. Cir. 1988)).

## 1. Anticipation

Pursuant to 35 U.S.C. § 102, a patent claim is invalid as anticipated if:

(1) the claimed invention was patented, described in a printed publication, or in public use, on sale, or otherwise available to the public before the effective filing date of the claimed invention; or

(2) the claimed invention was described in a patent issued under section 151, or in an application for patent published or deemed published under section 122(b), in which the patent or application, as the case may be,

names another inventor and was effectively filed before the effective filing date of the claimed invention.

35 U.S.C. § 102 (2012). "A patent is invalid for anticipation if a single prior art reference discloses each and every limitation of the claimed invention. Moreover, a prior art reference may anticipate without disclosing a feature of the claimed invention if that missing characteristic is necessarily present, or inherent, in the single anticipating reference." *Schering Corp. v. Geneva Pharm., Inc.*, 339 F.3d 1373, 1377 (Fed. Cir. 2003) (citations omitted).

#### 2. Obviousness

Section 103 of the Patent Act states:

A patent for a claimed invention may not be obtained, notwithstanding that the claimed invention is not identically disclosed as set forth in section 102, if the differences between the claimed invention and the prior art are such that the claimed invention as a whole would have been obvious before the effective filing date of the claimed invention to a person having ordinary skill in the art to which the claimed invention pertains. Patentability shall not be negated by the manner in which the invention was made.

35 U.S.C. § 103(a) (2011).

"Obviousness is a question of law based on underlying questions of fact." *Scanner Techs.*, 528 F.3d at 1379. The underlying factual determinations include: "(1) the scope and content of the prior art, (2) the level of ordinary skill in the art, (3) the differences between the claimed invention and the prior art, and (4) objective indicia of non-obviousness." *Id.* at 1380 (citing *Graham v. John Deere Co.*, 383 U.S. 1, 17-18 (1966)). These factual determinations are often referred to as the "*Graham* factors."

A relevant inquiry in determining the differences between the claimed invention and the prior art is whether there is a reason to combine the prior art references. *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 418-21 (2007). In *KSR*, the Supreme Court rejected the Federal Circuit's

rigid application of the teaching-suggestion-motivation test. While the Court stated that "it can be important to identify a reason that would have prompted a person of ordinary skill in the relevant field to combine the elements in the way the claimed new invention does," it described a more flexible analysis:

Often, it will be necessary for a court to look to interrelated teachings of multiple patents; the effects of demands known to the design community or present in the marketplace; and the background knowledge possessed by a person having ordinary skill in the art, all in order to determine whether there was an apparent reason to combine the known elements in the fashion claimed by the patent at issue . . . As our precedents make clear, however, the analysis need not seek out precise teachings directed to the specific subject matter of the challenged claim, for a court can take account of the inferences and creative steps that a person of ordinary skill in the art would employ.

*Id.* at 418. Applying *KSR*, the Federal Circuit has held that, where a patent challenger contends that a patent is invalid for obviousness based on a combination of prior art references, "the burden falls on the patent challenger to show by clear and convincing evidence that a person of ordinary skill in the art would have had reason to attempt to make the composition or device . . . and would have had a reasonable expectation of success in doing so." *PharmaStem*

Therapeutics, Inc. v. ViaCell, Inc., 491 F.3d 1342, 1360 (Fed. Cir. 2007).

In addition to demonstrating that a reason exists to combine prior art references, the challenger must demonstrate that the combination of prior art references discloses all of the limitations of the claims. *Hearing Components, Inc. v. Shure Inc.*, 600 F.3d 1357, 1373-1374 (Fed. Cir. 2010), *abrogated on other grounds by Nautilus, Inc. v. Biosig Instruments, Inc.*, 572 U.S. 898 (2014) (upholding finding of non-obviousness based on substantial evidence that the asserted combination of references failed to disclose a claim limitation); *Velander v. Garner*, 348 F.3d 1359, 1363 (Fed. Cir. 2003) (explaining that a requirement for a finding of obviousness is that "all the elements of an invention are found in a combination of prior art references").

# 3. Indefiniteness

"The Patent Act requires that a patent specification 'conclude with one or more claims particularly pointing out and distinctly claiming the subject matter which the applicant regards as [the] invention." *Nautilus, Inc. v. Biosig Instruments, Inc.,* 572 U.S. 898 (2014) (quoting 35 U.S.C. § 112, ¶ 2). "[T]he second paragraph of § 112 contains two requirements: first, [the claim] must set forth what the applicant regards as his invention, and second, it must do so with sufficient particularity and distinctness, *i.e.*, the claim must be sufficiently definite." *Allen Eng'g Corp. v. Bartell Indus., Inc,.* 299 F.3d 1336, 1348 (Fed. Cir. 2002) (citation and internal quotation marks omitted) (alteration in original). A claim does not satisfy the second requirement and is thereby indefinite "if read in light of the specification delineating the patent, and the prosecution history, [the claim] fail[s] to inform, with reasonable certainty, those skilled in the art about the scope of the invention." *Nautilus*, 534 U.S. at 901. Indefiniteness is a question of law, subject to a determination of underlying facts. *Akzo Nobel Coatings, Inc. v. Dow Chem. Co.*, 811 F.3d 1334, 1343-44 (Fed. Cir. 2016). The party challenging the validity of a claim bears the burden of establishing indefiniteness. *Id.*

# **D. Domestic Industry**

In patent-based proceedings under section 337, a complainant must establish that an industry "relating to the articles protected by the patent . . . exists or is in the process of being established" in the United States. 19 U.S.C. § 1337(a)(2). Under Commission precedent, the domestic industry requirement of section 337 consists of a "technical prong" and an "economic prong." *See, e.g., Alloc, Inc. v. Intl Trade Comm'n,* 342 F.3d 1361, 1375 (Fed. Cir. 2003).

To meet the technical prong, the complainant must establish that it practices at least one claim of the asserted patent. *Certain Point of Sale Terminals and Components Thereof*, Inv. No.

337-TA-524, Order No. 40 at 17-18, EDIS Doc. ID 230409 (Apr. 11, 2005). "The test for

satisfying the 'technical prong' of the industry requirement is essentially [the] same as that for

infringement, i.e., a comparison of domestic products to the asserted claims." Alloc, 342 F.3d at

1375.

With respect to the "economic prong," subsection (3) of Section 337(a) provides:

For purposes of paragraph (2), an industry in the United States shall be considered to exist if there is in the United States, with respect to the articles protected by the patent, copyright, trademark, mask work, or design concerned –

(A) significant investment in plant and equipment;

(B) significant employment of labor or capital; or

(C) substantial investment in its exploitation, including engineering, research and development, or licensing.

19 U.S.C. § 1337(a)(3).

Under subsections (A) and (B), the economic prong focuses on "articles protected by the patent." *Id.* Expenditures may be counted toward satisfaction of the domestic industry requirement "as long as those investments pertain to the complainant's industry with respect to the articles protected by the asserted IP rights." *Certain Television Sets, Television Receivers, Television Tuners, and Components Thereof,* Inv. No. 337-TA-910, Comm'n Op. at 68, 2015 WL 6755093, at \*36 (Oct. 30, 2015); *accord, e.g., Certain Marine Sonar Imaging Devices, Including Downscan and Sidescan Devices, Prods. Containing the Same, and Components Thereof,* Inv. No. 337-TA-921, Comm'n Op., 2016 WL 10987364, at \*40 (Jan. 6, 2016) ("Navico's allocation methodology reasonably approximates the warranty and technical customer support expenditures relating to the LSS-1 product.") (*citing Certain Ground Fault Circuit Interrupters and Prods. Containing Same,* Inv. No. 337-TA-739, Comm'n Op. at 74-75, 79-81, EDIS Doc. ID 482482 (June 8, 2012)).

Whether a complainant satisfies the economic prong is not analyzed according to a rigid mathematical formula. *Certain Male Prophylactic Devices*, Inv. No. 337-TA-546, Comm'n Op. at 39, EDIS Doc. ID 279161 (Aug. 1, 2007). The decision is made on a case-by-case basis and requires "an examination of the facts in each investigation, the article of commerce, and the realities of the marketplace." *Id.* A complainant must "provide context of the company's operations, the marketplace, or the industry in question necessary to understand whether the value of its domestic activities is significant or substantial." *Certain Carburetors and Products Containing Such Carburetors*, Inv. No. 337-TA-1123, Comm'n Op. at 19, EDIS Doc. ID 692517 (Oct. 28, 2019). However, there is no "minimum monetary expenditure," and a complainant does not "need to define or quantify the industry itself in absolute mathematical terms." *Stringed Musical Instruments*, Inv. No. 337-TA-586, Comm'n Op., 2009 WL 5134139, at \*16 (December 2009). "A precise accounting [of the complainant's domestic investments] is not necessary, as most people do not document their daily affairs in contemplation of possible litigation." *Id.* at 17.

#### IV. U.S. PATENT NO. 8,289,082

The '082 patent (JX-00006) is titled "Circuit and Method for Adjusting an Offset Output Current for an Input Current Amplifier" and names Armin Prohaska, Terje Saether, and Holger Vogelmann as inventors. '082 patent, cover. The '082 patent issued from an application filed on December 22, 2010, and claims priority to a provisional application filed on December 23, 2009. *Id*.

# A. Specification

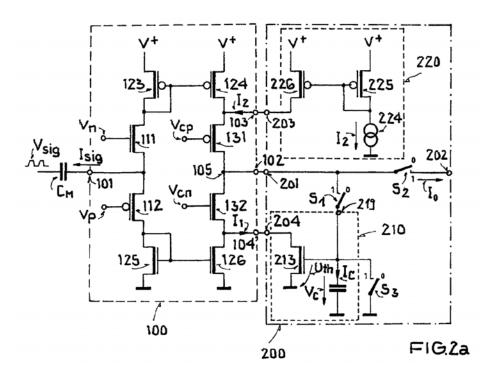

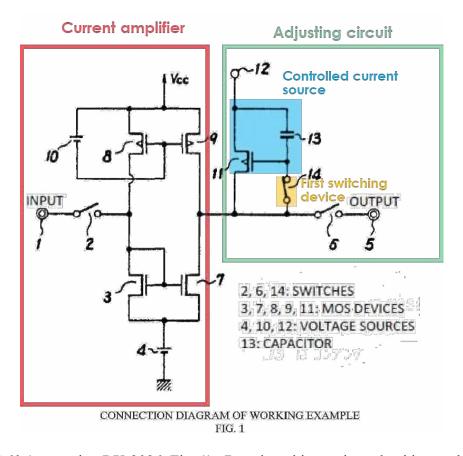

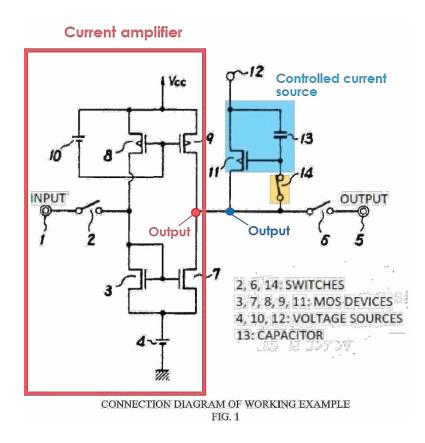

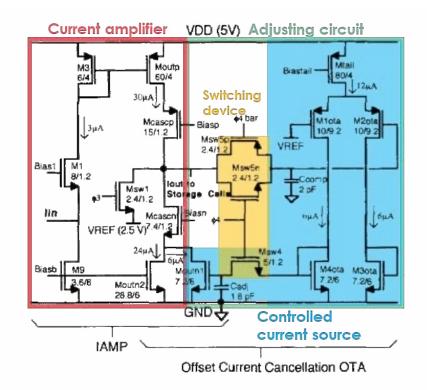

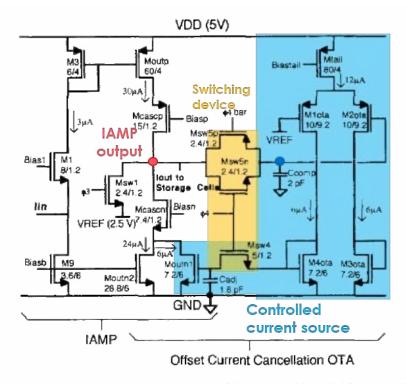

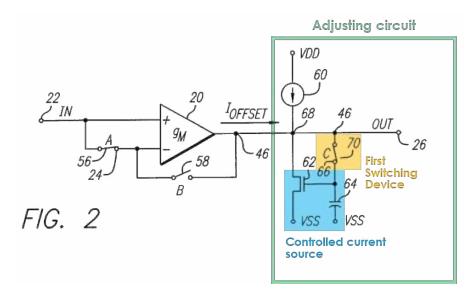

The '082 patent describes an invention for correcting an undesirable offset at the output of a current amplifier. '082 patent, Abstract. An exemplary embodiment shows a circuit diagram for an input current amplifier 100 with an adjusting circuit 200. *Id.* at 5:50-55.

*Id.* at Fig. 2a. "Because of process deviations during production," the output of the current amplifier 100 has an offset "Ioff." *Id.* at63-67. "Preferably, the adjusting circuit 200 is formed to adjust the offset Ioff of the current amplifier 100 to a minimum, preferably to the value of zero." *Id.* at 6:17-19. The adjusting circuit 200 is comprised of two current sources, a controlled current source 210 and a constant current source 220, which are both connected to the output of the current amplifier 100. *Id.* at 6:19-54.

The adjusting circuit further includes switching devices that can be opened and closed by signals from a control circuit for different states of operation. *Id.* at 7:36-67, 9:44-64. "In the closed state, first switching device S1 connects output 102 of adjusting circuit 200 to input 219

of controlled current source 210 and forms a control loop, whereby controlled current source 210 acts as a regulation element of this control loop." *Id.* at 7:45-49. "For regulation, second switching device S2 is open and disconnects output 202 of the circuit from output 102 of the adjusting circuit 200." *Id.* at 7:58-67. The capacitor 212 is charged by charging current Ic, which sets a current value of output current I1 such that "the offset Ioff active at output 102 is regulated to a minimum and thereby to a constant value, ideally zero." *Id.* at 8:1-13.

## B. Asserted claims

Arigna asserts claims 1, 13, 17, and 29 of the '082 patent. See Order No. 50 at 3 n.4. These

claims are recited below:

1. A circuit comprising:

a current amplifier; and

- an adjusting circuit configured to correct an offset of an output current of the current amplifier, the adjusting circuit having a controlled current source and a first switching device,

- wherein an output of the controlled current source is connectable to the current amplifier for producing an output current of the controlled current source in the current amplifier,

- wherein an input of the controlled current source is connectable by the first switching device of the adjusting circuit to an output of the current amplifier to form a regulation element of a control loop,

- wherein the input of the controlled current source is disconnected from the output of the current amplifier by the first switching device to form a holding element,

- wherein the controlled current source, acting as a regulation element in the control loop, is configured to regulate the offset to a minimum by setting a current value of the output current, and

- wherein the controlled current source, acting as a holding element, is configured to hold the current value, associated with the minimum, of the output current.

- 13. The circuit according to claim 1, further comprising a control circuit that is configured to control the first switching device and is connectable to a control terminal of the first switching device.

- 17. A method for correcting an offset of an output current of a current amplifier of a circuit, the method comprising:

- connecting a controlled current source to an output of the current amplifier via a first switching device, to form a regulation element of a control loop;

- regulating an offset to a minimum by setting a current value of the output current of the controlled current source when an input signal of the current amplifier has a constant value, the controlled current source acting as the regulation element; and

- disconnecting the controlled current source from the output of the current amplifier by the first switching device to form a holding element for holding the current value associated with the minimum of the output current.

- 29. The method according to claim 17, further comprising a control circuit that is configured to control the first switching device and is connectable to a control terminal of the first switching device.

# C. Claim Construction

The parties agreed to the construction of several claim terms in the '082 patent. See

Updated Joint Proposed Claim Construction Chart, EDIS Doc. ID 758271 (Dec. 9, 2021). The parties agreed that the term "current amplifier" has its "plain and ordinary meaning, *e.g.*, an amplifier that takes an input current and outputs an amplified current." *Id.* at 3. The parties agreed that the term "output of the current amplifier" has its plain and ordinary meaning, and the term "output current of a current amplifier" also has its "plain and ordinary meaning, *e.g.*, the amplified current output by the amplifier." *Id.* The term "the output current," as used in the asserted claims, was agreed to have its plain and ordinary meaning, *i.e.*, "the output current of the controlled current source." The term "offset of an output current of [the/a] current amplifier" was agreed to mean the "difference between observed and desired output current of [the/a] current amplifier." *Id.* at 4.

In the *Markman* order, the preamble of claim 17 was found to be limiting. Order No. 30 at 31-36. The parties were asked to provide additional briefing on the construction of the term

"input signal of the current amplifier." *Id.* at 36-39; *see* CIB at 12-18; RIB at 17-19; SIB at 33-37. The parties also dispute the construction of the terms "regulate the offset to a minimum" in claim 1 and "regulating the offset to a minimum" in claim 17. *See* Updated Joint Proposed Claim Construction Chart at 4; CIB at 18-22; RIB at 15-17; SIB at 40-43.

# 1. "input signal of the current amplifier"

The parties dispute the construction of the term "input signal of the current amplifier" in claim 17 of the '082 patent.

| <b>Complainant's Construction</b> | <b>Respondents'</b> Construction                                            | Staff's Construction       |

|-----------------------------------|-----------------------------------------------------------------------------|----------------------------|

| Plain and Ordinary Meaning        | "current supplied to the<br>current amplifier for current<br>amplification" | Plain and ordinary meaning |

The key dispute among the parties regarding this term is whether the "input signal of the current amplifier" can be a voltage signal, or whether it must be a current signal. Arigna submits that this term should have its plain and ordinary meaning, which it argues can refer to a voltage input to the claimed current amplifier. CIB at 12-18; CRB at 20-24. Respondents argue that the term refers to a current, and propose to construe "input signal of the current amplifier" to refer to the "current supplied to the current amplifier for current amplification." RIB at 17-19; RRB at 3-7. Staff agrees with Arigna that the "input signal of the current amplifier" is not necessarily a current. SIB at 33-37.

Claim 17 describes "regulating an offset to a minimum by setting a current value of the output current of the controlled current source when an input signal of the current amplifier has a constant value." Respondents argue that this "regulation phase" corresponds to a description in the specification where the input current signal has a constant value, preferably zero, and this is summed with the output current and constant current to determine the appropriate level of offset

correction. '082 patent at 7:58-67; *see* RIB at 17-18. "The regulation occurs when an input signal of the current amplifier has a constant value . . . Ideally, the direct current value, present at the input of the current amplifier, of the input signal is zero." '082 patent at 2:23-30 (cited in RIB at 18). Respondents' expert Dr. Sinenian submits that "what a person of ordinary skill would understand in reading this part of the specification is that during this regulation phase, the input signal is a current." Tr. (Sinenian) at 1066:9-1068:17.

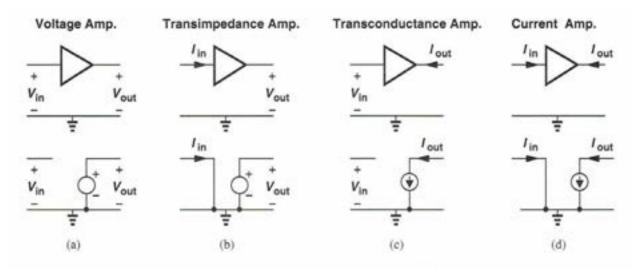

Dr. Sinenian further submits that a "current amplifier" is one type of fundamental amplifier, referencing electrical engineering textbooks (including the figure reproduced below). *Id.* at 1033:4-1038:14.; RDX-0005C.4. He explains that "a current amplifier has a current signal as its input." *Id.* at 1036:25-1037:16.

Figure 8.11 Types of amplifiers along with their idealized models.

RX-1629 (Razavi, "Design of Analog CMOS Integrated Circuits") at 254; *see also* RX-1630 (Sedra and Smith, "Microelectronic Circuits") at 28. The '082 patent specification states: "Current amplifier 100 has a current input and a current output." '082 patent at 5:34-35; *see* RIB at 17. Arigna's expert Dr. Sechen agrees that a current amplifier "is an amplifier that receives an input current and outputs a current that is larger than the input current." Tr. (Sechen) at 158:24-

159:3. Staff agrees that this understanding of a "current amplifier" is consistent with the specification and the extrinsic evidence. SIB at 29-32.

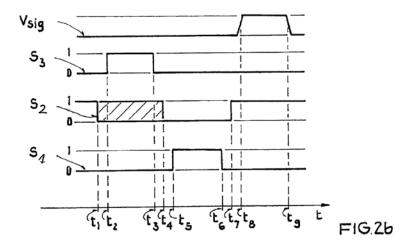

Although the parties agree that a "current amplifier" receives an input current, Arigna argues that the claim language "input signal of the current amplifier" is broad enough to encompass other inputs, including voltage signals. CIB at 12-18; CRB at 20-24. Dr. Sechen submits that this is consistent with the specification of the '082 patent, which identifies a voltage signal "Vsig" as an input signal that is used to create the "Isig" current that is input to the current amplifier 100. Tr. (Sechen) at 160:24-161:19. He submits that when "Vsig" is constant, the corresponding "Isig" will be zero. *Id.* at 249:8-16. Dr. Sechen suggests that the voltage signal "Vsig" is constant during the "regulation period" depicted in Figure 2b of the '082 patent, a timing diagram that describes the operation of several switches. *Id.* at 248:8-250:2.

'082 patent, Fig. 2b. Arigna identifies a statement in the specification that states: "For regulation, second switching device S2 is open." *Id.* at 7:58-60. Arigna submits that in Figure 2b, Vsig is constant between t1 and t7, when S2 is open. CIB at 16. Arigna argues that Respondents' proposed construction would exclude the embodiment depicted in Figure 2b by

limiting the "input signal" to the current signal Isig, because Isig is zero and a zero signal cannot be amplified. *Id.* at 17-18.

Respondents argue that Vsig cannot be the claimed "input signal" because it is not input to the current amplifier 100. RIB at 18-19. Dr. Sinenian explains that the role of Vsig is only to power the capacitor Cm, which generates the signal Isig when the user interacts with the touchscreen. Tr. (Sinenian) at 1068:25-1069:17. He also testifies that in the device depicted in the specification, Vsig does not "enter the amplifier" and "does not carry information that is amplified by the current amplifier." *Id.* at 1069:18-21. As described in the specification in reference to Figure 2b, "[b]etween time points t8 and t9, a voltage signal Vsig is sent to a capacitor Cm of a touch screen. If the screen is touched, the capacitor Cm is changed and moreover a signal current Isig is produced, which flows as an input current via input 101 into/out of input current amplifier 100 and is amplified by input current amplifier 100." '082 patent at 8:57-62. Respondents submit that a zero Isig signal as input to the current amplifier during the regulation phase is consistent with the explicit disclosure of the specification. RRB at 5-6; '082 patent at 7:58-61 ("For regulation ... [t]he input signal current Isig is zero in this case.").

Staff agrees with Respondents that the "input signal" of the current amplifier described in the preferred embodiments of the specification is "the current that is input into the amplifier for current amplification" (SIB at 33), but Staff argues that the scope of the claim should not be limited to the preferred embodiment. SIB at 33-37. Staff identifies disclosures in the specification that use the terms "input" and "signal" to refer to other types of electrical inputs and signals. *Id.* at 34. In particular, the specification describes "voltage signal Vsig" that is "sent to a capacitor Cm of a touch screen." '082 patent at 8:57-58. In addition, there is a "control signal" sent by control circuit 300 to switching device S2 and S3. *Id.* at 9:34-41. The

specification also refers to "a control voltage at the control input of the transistor" in the controlled current source. *Id.* at 2:60-62. Staff argues that claim 17 uses the terms "output current" and "current value" but does not refer to the "input signal" as an "input current," suggesting that the "input signal" could be something other than a current. SIB at 34-35. Staff argues that Respondents' construction would improperly limit the claimed current amplifier to only one input. *Id.* at 36-37.

In consideration of the parties' arguments, the undersigned finds that the term "input signal of the current amplifier," viewed in light of the claim language, specification and the plain and ordinary meaning of "current amplifier," refers to a current signal. With regard to the current amplifier, the specification of the '082 patent only uses the term "input signal" to refer to a current, which is identified as "Isig." *See* '082 patent at 1:64-67, 2:10-13, 2:26-32, 2:37-40, 7:2-5, 7:58-61. In the context of regulating an offset to a minimum, the specification explains why this "input signal" must be constant or zero:

The regulation occurs when an input signal of the current amplifier has a constant value. Therefore, only a direct current value but not an alternating current is present at the input of the current amplifier during the regulation. Ideally, the direct current value, present at the input of the current amplifier, of the input signal is zero.

*Id.* at 2:26-32.<sup>4</sup> In the alleged invention disclosed in the '082 patent, the amount of offset to be corrected is determined when the input signal of the current amplifier is constant or zero, because this permits one to expose the undesired offset current and correct for it. *See* Tr. (Sinenian) at 1066:9-1067:15. There is no embodiment of the invention disclosed in the '082 patent where

<sup>&</sup>lt;sup>4</sup> See also id. at 7:58-65 ("For regulation, second switching device S2 is open and disconnects output 202 of the circuit from output 102 of adjusting circuit 200. The input signal current Isig is zero in this case. As a result, the resulting current, which results from the summation of the output current of first current mirror 123, 124, of the output current of second current mirror 125, 126, and of constant current I2, flows out at output 102 of input current amplifier 100.").

regulating an offset of the current amplifier is associated with keeping a different input signal of the current amplifier constant, such as the control signals identified by Staff. *See* SIB at 33 ("in the preferred embodiments, the 'input signal' is identified as the current that is input into the amplifier for current amplification."). The claim describes "regulating an offset to a minimum by setting a current value of the output current of the controlled current source when an input signal of the current amplifier has a constant value," and the only "input signal" that makes sense in the context of the specification, the claim language, and the accepted meaning of "current amplifier," is a current signal. *See* Tr. (Sinenian) at 1033:4-1038:14; RX-1629 (Razavi, "Design of Analog CMOS Integrated Circuits") at 254; RX-1630 (Sedra and Smith, "Microelectronic Circuits") at 28; '082 patent at 5:34-35; Tr. (Sechen) at 158:24-159:3 (current amplifier "is an amplifier that receives *an input current* and outputs a current that is larger than the input current") (emphasis added).

Arigna's arguments regarding "Vsig" are unpersuasive because "Vsig" is not input to the current amplifier in the specification. *See* '082 patent at Fig. 2a; *see also* Tr. at 1069:22-1070:1 (Q: "Does Vsig even enter the current amplifier?" A (Sinenian): "No. Again, Cm represents the touchscreen controller in this case. I believe the specification calls that out. So it is not even connected to the input directly. It is connected to the touchscreen controller."); SIB at 33.

While the undersigned agrees with Staff that the terms "input" and "signal," in isolation, can have broader meanings in the art, "[t]he construction that stays true to the claim language and most naturally aligns with the patent's description of the invention" requires an input signal that is a current. *Renishaw PLC v. Marposs Societa' per Azioni*, 158 F.3d 1243, 1250 (Fed. Cir. 1998). In addition, the undersigned is persuaded by Dr. Sinenian's testimony that one of ordinary skill in the art would read the term "input signal of the current amplifier" in the context

of the '082 patent to refer to a current signal. *See* Tr. (Sinenian) at 1066:9-1068:17. This construction, moreover, does not mean that the term "input signal" lacks any meaning beyond being an "input current." Rather the word "signal" indicates that it is an input current carrying information of interest. *See* SMX-0006, Penguin Dictionary of Electronics, 3<sup>rd</sup> ed. (1998) (EDIS Doc. ID 756132) at 515 ("signal" is a variable electrical parameter "used to convey information"); Tr. (Sinenian) at 1033:10 ("a signal carries information of interest"); Tr. (Souri) at 1168:6-13 (stating that signals carry or can carry "meaningful information" and distinguishing between "input signal of the current amplifier" and noise); SIB at 52 (stating that a "signal" is used to convey "some information of interest" and distinguishing between a "current signal" and a current value derived for a voltage signal through Ohm's law).

For these reasons, the term "input signal of the current amplifier," as used in claim 17 of the '082 patent, refers to a current, not a voltage.<sup>5</sup>

# "regulat[ing] the offset to a minimum"

The parties dispute the construction of the terms "regulate the offset to a minimum" in claim 1 and "regulating the offset to a minimum" in claim 17 of the '082 patent.

| <b>Complainant's Construction</b>                                                                     | <b>Respondents' Construction</b> | Staff's Construction                         |

|-------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------|

| "adjust the offset to a value<br>closer to zero" / "adjusting an<br>offset to a value closer to zero" | Indefinite                       | "regulating an offset to at or<br>near zero" |

<sup>&</sup>lt;sup>5</sup> For purposes of assessing the disputed infringement and invalidity issues, it is unnecessary to resolve other disputes among the parties regarding the proper construction—*e.g.*, whether the current that is the "input signal of the current amplifier" must undergo current amplification during the regulation phase. *See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co. Ltd. Matal.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017) ("we need only construe terms that are in controversy, and only to the extent necessary to resolve the controversy") (internal citations omitted); *see also Choon's Design, LLC v. Idea Village Prods. Corp.*, 776 Fed. Appx. 691 n.3 (Fed. Cir. June 24, 2019).

Respondents contend that the terms "regulate the offset to a minimum" and "regulating the offset to a minimum" are indefinite. RIB at 15-17; RRB at 7-8. Arigna proposes to construe these terms to mean "adjust the offset to a value closer to zero" or "adjusting an offset to a value closer to zero." CIB at 18-22; CRB at 24-28. Staff proposes its own construction of these terms: "regulating an offset to at or near zero." SIB at 40-43; SRB at 10-11.

Respondents argue that these terms are indefinite because there are no objective boundaries for the claimed "minimum." RIB at 15-17; RRB at 7-8. Respondents' expert Dr. Souri offered his opinion that these terms are indefinite because there is no indication in the specification that provides reasonable certainty for the range of values that would be a "minimum" and submits that this is not a term of art. Tr. (Souri) at 1184:10-1185:14.

Arigna argues that these terms are not indefinite because the specification explicitly provides that "[t]he minimum offset is achieved when the output current from a current amplifier has reached a steady state; therefore it is substantially constant, ideally zero." '082 patent at 2:3-6. Dr. Sechen testified at the hearing that the term "steady state" means "when current and voltage values are no longer varying. They're constant, in other words." Tr. (Sechen) at 206:14-20. Dr. Sechen further explained that "at the schematic level, if you were to simulate the circuit with a standard industry circuit simulator like HSPICE or what have you, you would find that the offset would be exactly zero. Of course, where a real circuit fabricated out of real components, the offset would be close to zero, in fact." *Id.* at 231:16-232:6.

Arigna proposes to construe these terms to cover any adjustment "closer to zero," relying on the disclosures in the specification providing that "[t]he minimum offset is achieved when the output current from a current amplifier has reached a steady state; therefore it is substantially constant, ideally zero." '082 patent at 2:3-6. In a specific embodiment, the specification

describes the offset "regulated to a minimum and thereby to a constant value, ideally zero." *Id.* at 8:8-10. Arigna argues that these disclosures recognize that the claimed minimum does not need to be at or near zero—the only requirement is that the offset value is closer to zero. CRB at 27-28.

Staff agrees with Arigna that these terms are not indefinite, finding reasonable certainty for this limitation in view of the claims and specification. SIB at 76-77. Staff proposes to construe these terms to mean "regulating an offset to at or near zero" based on the same disclosures in the specification cited by Arigna. *Id.* at 40-43. Staff highlights the disclosures in the specification describing the minimum value as "ideally zero." '082 patent at 2:3-6, 8:10-11; *see also id.* at 6:17-19 ("preferably . . . zero"). The specification also describes this minimum as a "negligible offset." *Id.* at 7:31-35. Staff argues that Arigna's construction would read the term "minimum" out of the claim language, requiring only a reduction without reaching the lowest value or near zero, as described in the specification. SIB at 42-43. At the hearing, Dr. Souri joined in Staff's criticism of Arigna's proposed construction, offering his opinion that it would rewrite the claim to be regulating towards a minimum rather than "to a minimum." Tr. (Souri) at 1185:13-24.

In consideration of the parties' arguments, the undersigned finds that the terms "regulate the offset to a minimum" and "regulating the offset to a minimum" are not indefinite and shall be construed to mean "regulating an offset to at or near zero." The specification describes the minimum to be "ideally zero" or "preferably to the value of zero." '082 patent at 2:3-6, 6:17-19. It further describes the minimum as providing "no or only a negligible offset." *See id.* at 7:31-35 (stating that in certain embodiments where "a regulation of the offset Ioff to a minimum is possible . . . no or only a negligible offset Ioff interferes with the output signal Io of the circuit").

These disclosures are sufficient to "inform those skilled in the art about the scope of the invention with reasonable certainty." Nautilus, Inc. v. Biosig Instruments, Inc., 572 U.S. 898, 901 (2014). As recognized by Dr. Sechen, circuits meeting this limitation would achieve an offset of exactly zero "at the schematic level" using "a standard industry circuit simulator," but in "a real circuit fabricated out of real components, the offset would be close to zero, in fact." Tr. (Sechen) at 231:16-232:6; see also id. at 233:1-8. Staff's construction, supported by the testimony of Dr. Sechen, recognizes the inherent manufacturing imperfections and real-world engineering tolerances that may prevent the offset from reaching precisely zero, while providing reasonable certainty and remaining true to the claim language and the specification. See SIB at 77; cf. Pulse Electronics, Inc. v. U.D. Electronic Corp., 860 Fed. Appx. 735, 739 (Fed. Cir. July 1, 2021) ("desired effect of changing direction by approximately 90 degrees" not indefinite where PTAB had found that "approximately 90 degrees" means "near or equal to 90 degrees' (to account, e.g., for 'manufacturing tolerances')" and "desired effect" has "a clear and objective meaning: that the conductors curve or change direction by approximately 90 degrees").<sup>6</sup> Here, unlike the situation addressed by the Federal Circuit in Berkheimer v. HP Inc. (see RRB at 7-8), there is expert testimony providing guidance as to the meaning of this limitation. 881 F.3d 1360, 1363-64 (Fed. Cir. 2018) (finding no clear error in indefiniteness finding "in light of the

<sup>&</sup>lt;sup>6</sup> Complainant's proposed construction ("a value closer to zero") appears disconnected from its underlying argument that a "minimum" must be a steady state or "substantially constant" value. . Complainant's arguments regarding "substantially constant value" do not appear in its proposed construction. *See also* SIB at 42-43. In addition, the only support cited by Complainant for its argument regarding "closer to zero" is the testimony of Dr. Sechen, who testified that the value should be "close" (not "closer") to zero in view of real-world engineering issues. *See* CIB at 20 (citing Tr. (Sechen) at 232:7-233:8). The testimony of Dr. Souri, Respondents' expert, regarding Staff's proposed construction is conclusory and does not address the issue of real-world tolerances, and thus fails to meet the clear and convincing standard for indefiniteness. For these reasons and those discussed above, Complainant's proposed construction and Respondents' indefiniteness argument are rejected.

evidence in this case" where patentee offered no expert testimony); Tr. (Sechen) at 231:16-233:8.

For these reasons, the proper construction of "regulate the offset to a minimum" and "regulating the offset to a minimum" is "regulating an offset to at or near zero." The evidence does not show clearly and convincingly that the term is indefinite.

# **D.** Level of Ordinary Skill in the Art

In the *Markman* order, the level of ordinary skill in the art was found to be a bachelor's degree in electrical engineering or a similar field, and approximately two years of industry or academic experience designing or analyzing electronic circuits, including experience with amplifiers. Order No. 30 at 10-11.

# E. Infringement

Arigna's infringement allegations for the '082 patent are based on Dr. Sechen's analysis of the Analog Devices AD8417 chip used in the Hella 48V Converter of certain Mercedes vehicles and the Analog Devices AD8418 chip used in the Bosch 48V Converter of certain Volkswagen vehicles and in the Bosch LEB450 Inverter of certain BMW vehicles. CIB at 22-24; Tr. (Sechen) at 167:24-170:17. There are no material differences between the AD8417 and AD8418 chips for the purposes of the infringement analysis. *See* CIB at 23; SIB at 44 n.10; Tr. at 170:18-23 (Sechen), 1086:17-1087:8 (Sinenian).

# 1. Claim 1

Arigna alleges that components in the AD8417 and AD8418 chips meet each of the limitations of claim 1 of the '082 patent. CIB at 24-49; CRB at 28-51. Respondents and Staff dispute infringement of the "current amplifier" limitation, as discussed below. *See* RIB at 22-41; RRB at 10-22; SIB at 44-55; SRB at 12-18. Respondents also dispute infringement of the

"output current" limitation, because there is no "current amplifier." RIB at 41-42. Respondents further dispute infringement of the limitation requiring regulation of an offset "to a minimum." *Id.* at 41.

# a. "A circuit comprising"

There is no dispute that the AD8417 and AD8418 chips comprise circuits. CIB at 24-25. Dr. Sechen identifies schematics and datasheets describing the circuitry of the AD8417 and AD8418 chips. Tr. (Sechen) at 216:7-13, 218:10-13; CX-00594C (AD8418 schematic); CX-00627C (AD8417 schematic).

# b. "a current amplifier"

Arigna relies on Dr. Sechen's identification of a "current amplifier" in the AD8417 and AD8418 chips. CIB at 25-34; Tr. (Sechen) at 174:23-198:15. Specifically, Dr. Sechen identifies a "current amplifier" that he testified includes a differential current within the

of the AD8418 as the input to the "current amplifier" and a current provided to the

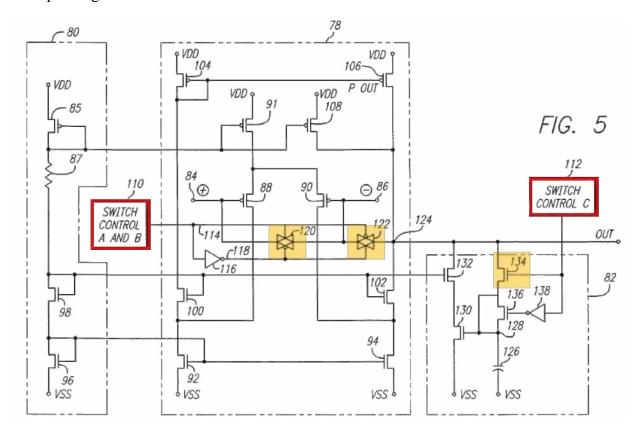

block as the output of the "current amplifier." Tr. (Sechen) at 175:7-25. A "top-level schematic" for the accused chips is shown below:

| CDX-001C-27; CX-00594C; CX-00627C; Tr. (Sechen) at 174:8-175:25. Within the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (shown in CDX-001C-29 below), Dr. Sechen states that the asserted input current is the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| result of converting the voltage signals at the second sec |

| identifies as Tr. (Sechen) at 176:1-181:10. He submits that the conversion of voltage to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |